in pull-down NMOS network, AND means series, so A.B series

in pull-down NMOS network, AND means series, so C.D series

in pull-up PMOS network, interchange parallel and series for pull-down network

In pull-down network,

AND --> Series

OR --> Parallel

In pull-up network,

opposite of pull-down network

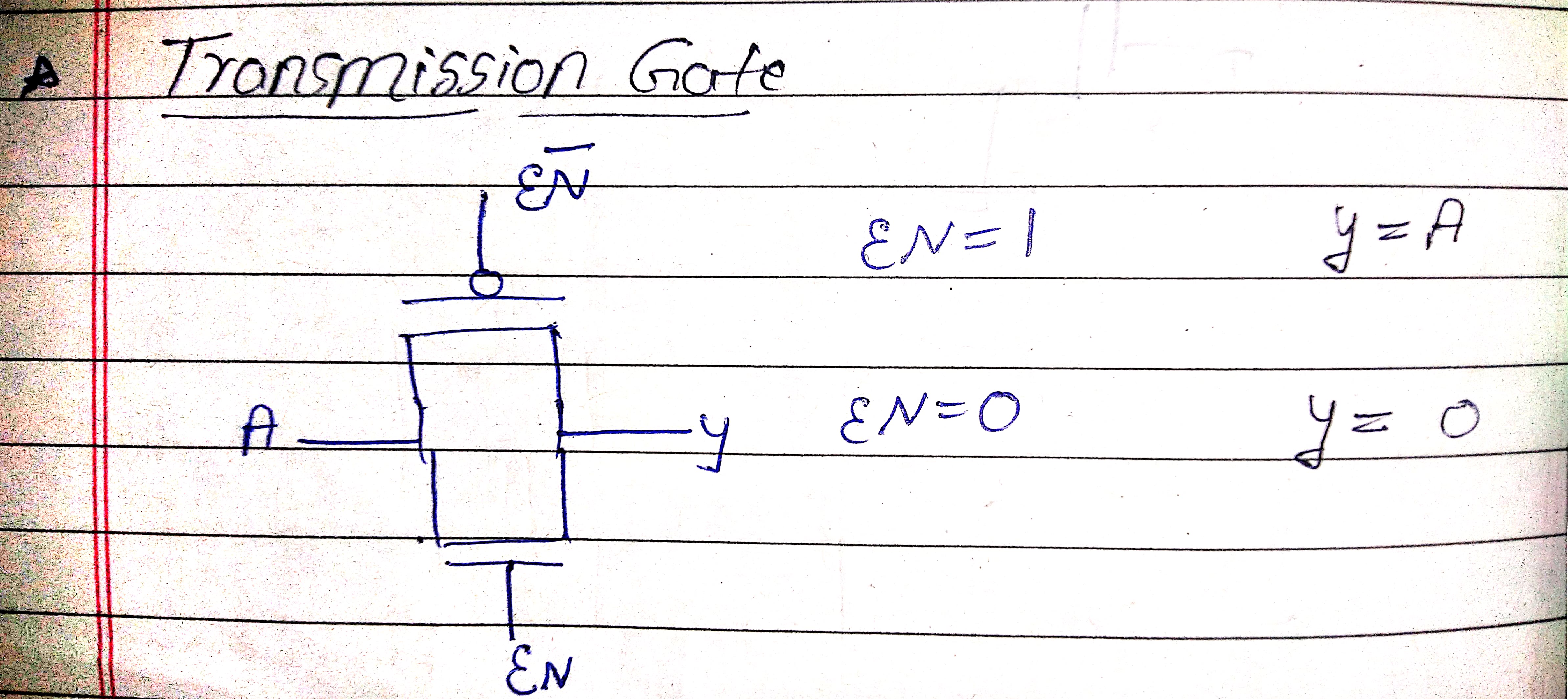

NMOS pass transistor can pull down to a negative rail but can pull up to a threshold voltage below positive rail

PMOS pass transistor can pull up to a positive rail but can pull down to a threshold voltage above negative rail

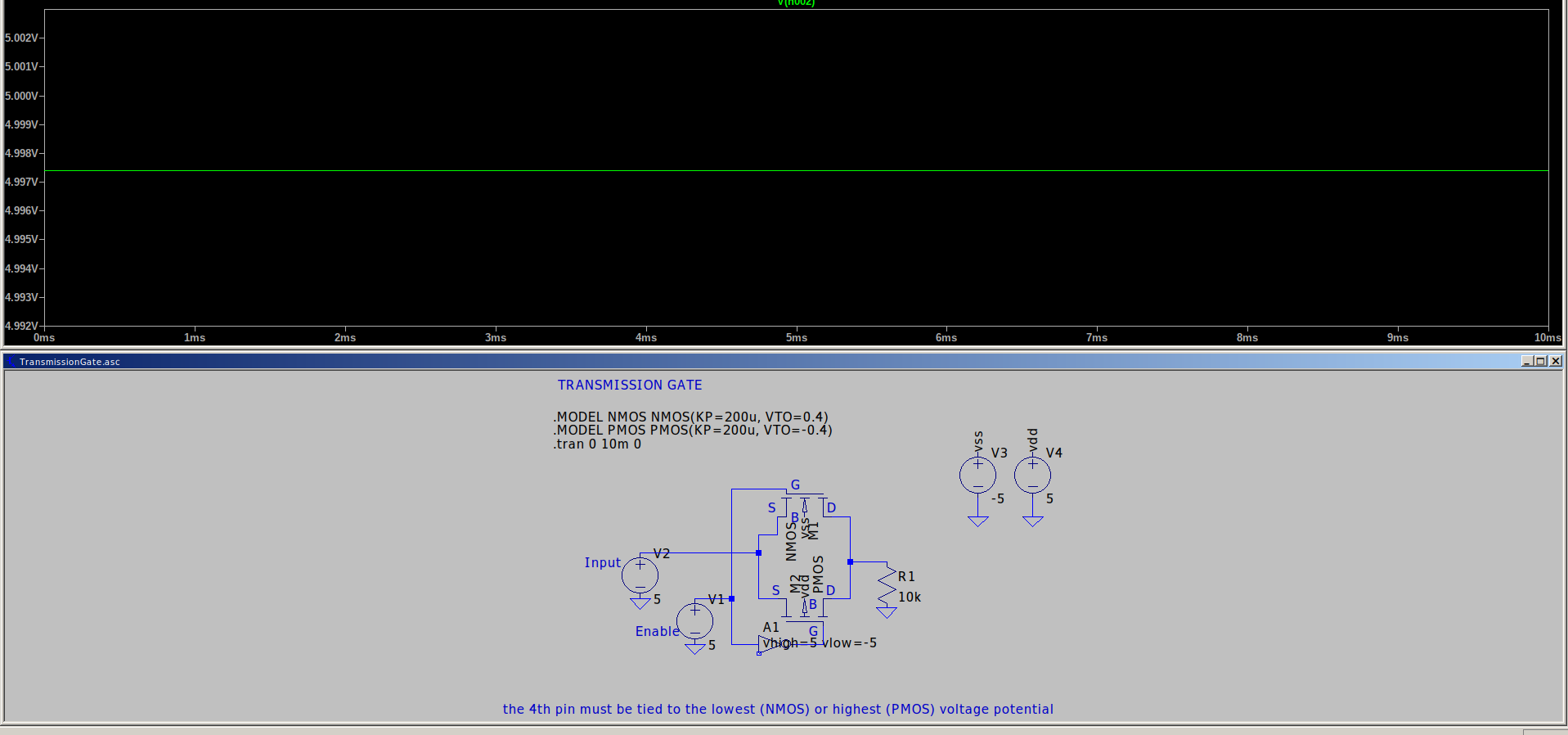

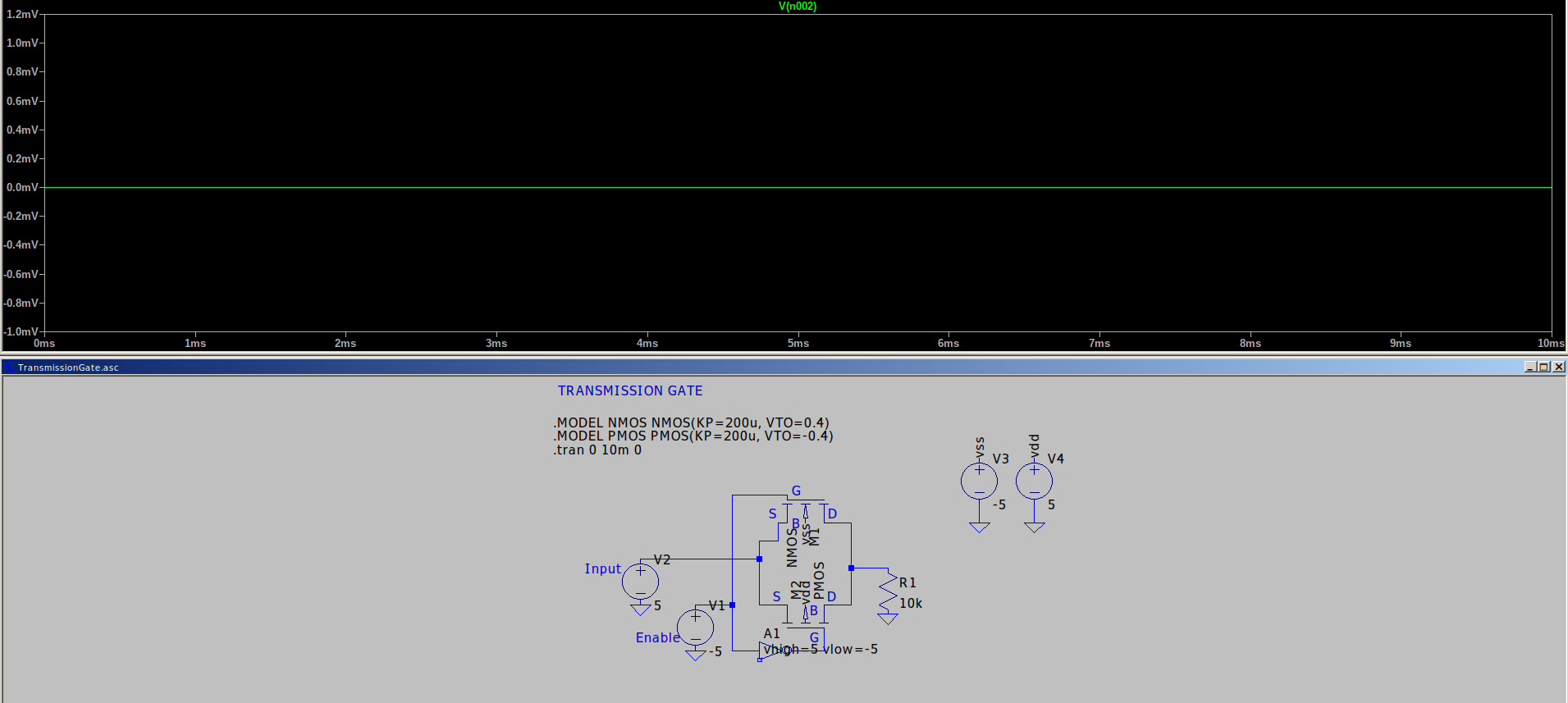

the 4th pin must be tied to the lowest (NMOS) or highest (PMOS) voltage potential

images

spice_works

inverter_magic.spice

inverter_magic.magc

inverter_magic.ext

magic_ngspice_tut.txt